[ترجمه] مقایسه عملکرد گیت های دیجیتال با استفاده از CMOS و منطق ترانزیستور گذر در نرم افزار CADENCE VIRTUOSO

چکیده

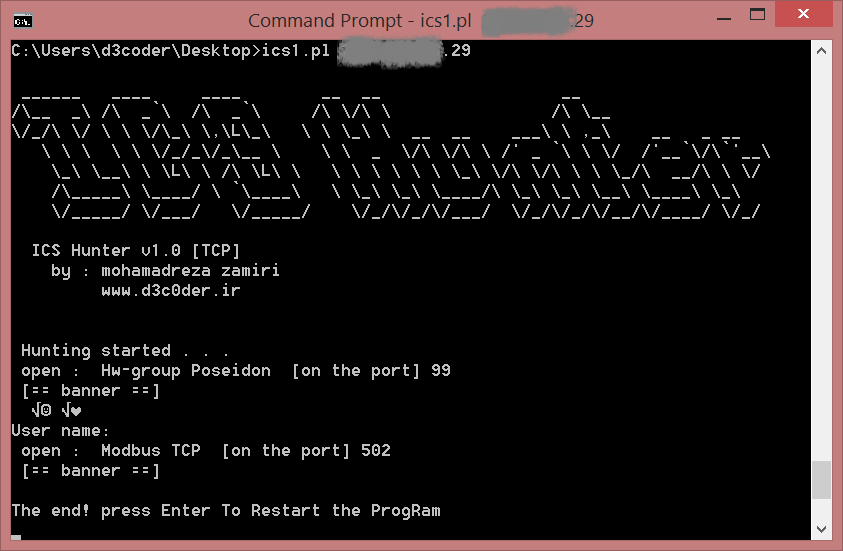

این مقاله در مورد پیاده سازی گیت ها با استفاده از فناوری 0.18μm در نرم افزار Cadence Virtuoso 6.14 و بهینه سازی عواملی همچون اتلاف توان، اندازه و تعداد ترانزیستورهای موجود در مدارهای دیجیتال صحبت میکند. بنابراین، بهینه سازی این اجزا در نهایت منجر به استفاده بهینه از انواع منابع خواهد شد. همچنین این پروژه بر روی ساختارهای نوآورانه transistor-transistor logic (TTL) از اجزاء دیجیتالی مختلف از جمله گیت AND، OR و غیره بر مبنای منطق ترانزیستور گذر اطلاعاتی را ارائه میکند. این ساختارها از ترانزیستورهای کمتری استفاده می کنند و توان کمتری را در مقایسه با دستگاه های مشابه که توسط منطق CMOS معمولی پیاده سازی شده اند، تلف میکنند.

مقدمه

از آنجا که منطق ترانزیستور گذر (PTL) امکان پیاده سازی مدارات با سرعت بالا و توان کم را در برنامه های اصلی میدهد، بسیار محبوب شده است. شمار زیادی از این مدارها با عملکرد بهینه شده از منظر سرعت و کارایی توان توسعه داده شده اند. همچنین روش های ترکیبی که بطور کلی پیاده سازی های ترانزیستور گذر را هدف قرار میدهند، استفاده از منطق ترانزیستور گذر منجر به کاهش تعداد ترانزیستور و ظرفیت های گره کوچک تر می شود و در نتیجه نیاز به مساحت، زمان های rise و fall و اتلاف توان را کاهش میدهد. از نقطه نظر پیاده سازی، طراحی کارآمد مدارهای مجتمع به شدت به ابزارهای CAD وابسته است که میتواند عملکرد آنها را سریع و دقیق برآورد کند. از آنجایی که تعداد ترانزیستور در مدارهای مجتمع در حال افزایش یافتن است، به شدت به روش های مدل سازی نیاز است که بتوانند دقت کافی را ارائه دهند اما نسبت به ابزارهای مبتنی بر روش های عددی سریع تر باشند.

- ۰ نظر

- ۱۳ فروردين ۹۷ ، ۱۸:۱۱