[ترجمه] مقایسه عملکرد گیت های دیجیتال با استفاده از CMOS و منطق ترانزیستور گذر در نرم افزار CADENCE VIRTUOSO

چکیده

این مقاله در مورد پیاده سازی گیت ها با استفاده از فناوری 0.18μm در نرم افزار Cadence Virtuoso 6.14 و بهینه سازی عواملی همچون اتلاف توان، اندازه و تعداد ترانزیستورهای موجود در مدارهای دیجیتال صحبت میکند. بنابراین، بهینه سازی این اجزا در نهایت منجر به استفاده بهینه از انواع منابع خواهد شد. همچنین این پروژه بر روی ساختارهای نوآورانه transistor-transistor logic (TTL) از اجزاء دیجیتالی مختلف از جمله گیت AND، OR و غیره بر مبنای منطق ترانزیستور گذر اطلاعاتی را ارائه میکند. این ساختارها از ترانزیستورهای کمتری استفاده می کنند و توان کمتری را در مقایسه با دستگاه های مشابه که توسط منطق CMOS معمولی پیاده سازی شده اند، تلف میکنند.

مقدمه

از آنجا که منطق ترانزیستور گذر (PTL) امکان پیاده سازی مدارات با سرعت بالا و توان کم را در برنامه های اصلی میدهد، بسیار محبوب شده است. شمار زیادی از این مدارها با عملکرد بهینه شده از منظر سرعت و کارایی توان توسعه داده شده اند. همچنین روش های ترکیبی که بطور کلی پیاده سازی های ترانزیستور گذر را هدف قرار میدهند، استفاده از منطق ترانزیستور گذر منجر به کاهش تعداد ترانزیستور و ظرفیت های گره کوچک تر می شود و در نتیجه نیاز به مساحت، زمان های rise و fall و اتلاف توان را کاهش میدهد. از نقطه نظر پیاده سازی، طراحی کارآمد مدارهای مجتمع به شدت به ابزارهای CAD وابسته است که میتواند عملکرد آنها را سریع و دقیق برآورد کند. از آنجایی که تعداد ترانزیستور در مدارهای مجتمع در حال افزایش یافتن است، به شدت به روش های مدل سازی نیاز است که بتوانند دقت کافی را ارائه دهند اما نسبت به ابزارهای مبتنی بر روش های عددی سریع تر باشند.

سبک های منطق[1]

سبک منطق مورد استفاده در گیت های منطقی اساسا بر سرعت، اندازه، اتلاف توان و پیچیدگی سیم کشی یک مدار تاثیر می گذارد. تاخیر مدار توسط تعداد سطح معکوس، تعداد ترانزیستورهای سری، اندازه ترانزیستور تعیین می شود. اندازه مدار به تعداد ترانزیستورها و اندازه آنها، و همچنین به پیچیدگی سیم کشی بستگی دارد.

اتلاف توان توسط سوئیچینگ و ظرفیت های گره (ساخته شده از گیت، diffusion، و ظرفیت های سیمی) تعیین می شود، مورد دوم تابعی از همین پارامترها است که همچنین سایز مدار را نیز کنترل میکند. در نهایت، پیچیدگی سیم کشی توسط تعداد اتصالات و طول آنها تعیین می شود. تمام این مشخصه ها ممکن است به طور قابل توجهی از یک سبک منطق به دیگری متفاوت باشد و بنابراین انتخاب مناسب سبک منطق برای عملکرد مدار ضروری است. با توجه به این که تکنیک های طراحی مبتنی بر سلول (به عنوان مثال، سلول های استاندارد) و منطق ترکیبی مورد بررسی قرار گرفتند، سادگی در استفاده و عمومیت گیت های منطقی نیز اهمیت دارند.

سبک طراحی PTL به عنوان یک جایگزین امیدوارکننده برای CMOS معمولی، برای طراحی کم قدرت ظهور کرده است. یک دستگاه مبتنی بر منطق ترانزیستور گذر در مقایسه با یک دستگاه مبتنی بر منطق CMOS که بر اساس همان منطق پیاده سازی شده، توان کمتری مصرف میکند.

*(1)

در اینجا avgP میانگین اتلاف توان، Tiα عامل گره انتقال گره گذر، iC ظرفیت پارازیتی مرتبط با هر گره، iV ولتاژ گره، DDV ولتاژ منبع تغذیه و CLKf فرکانس ساعت است.

از معادله 1، روشن است که متوسط اتلاف توان هر دستگاه به طور مستقیم وابسته به تعداد گره ها (یعنی ترانزیستورها) و ولتاژ منبع تغذیه است. با کاهش هر یک از آنها ما می توانیم میانگین اتلاف توان دستگاه ها را کاهش دهیم. منطق ترانزیستور گذر نه تنها اتلاف توان را کاهش می دهد، بلکه باعث کاهش اندازه کلی تراشه، کارآمدتر و ارزان تر شدن آن میشود.در اینجا یک مثال از اجرای دو گیت منطقی NOT و OR با استفاده از منطق ترانزیستور گذر و CMOS و مقایسه نتایج آن ها قابل مشاهده است.

نتایج تجربی

در این مقاله طراحی PTL از AND، OR و NAND در نظر گرفته شده است. پارامترهای مورد نظر اتلاف توان، زمان افزایش، زمان سقوط و تاخیر انتشار هستند.

|

پارامترها |

مقدار CMOS |

مقدار PASS |

|

فناوری (طول) |

180nm |

180nm |

|

ولتاژ منبع تغذیه (VDD) |

1.8 Volts |

1.8 Volts |

|

عرض |

Pmos(4um) Nmos(2um) |

Pmos(4um) Nmos(2um) |

|

زمان افزایش (I / P 10P) |

0.8415ns |

0.11663ns |

|

زمان سقوط (I / P 10P) |

0.6080ns |

0.0101475ns |

|

تاخیر انتشار (I / P 0) |

0.61415ns |

0.007075ns |

|

اتلاف توان |

4.1579513*10^-11 W |

9.3531277*10^-16 W |

|

تعداد ترانزیستورها |

6 |

2 |

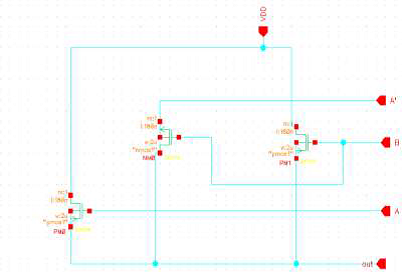

تصویر 2 – گیت OR

|

پارامترها |

مقدار CMOS |

مقدار PASS |

|

فناوری (طول) |

180nm |

180nm |

|

ولتاژ منبع تغذیه (VDD) |

1.8 Volts |

1.8 Volts |

|

عرض |

Pmos(4um) Nmos(2um) |

Pmos(4um) Nmos(2um) |

|

زمان افزایش (I / P 10P) |

0.06834ns |

0.0116ns |

|

زمان سقوط (I / P 10P) |

0.082006ns |

0.00835ns |

|

تاخیر انتشار (I / P 0) |

0.0638165ns |

0.00971245ns |

|

اتلاف توان |

2.7833563*10^-11 W |

9.3531277*10^-11 W |

|

تعداد ترانزیستورها |

6 |

2 |

تصویر 3 – گیت NAND

|

پارامترها |

مقدار CMOS |

مقدار PASS |

|

فناوری (طول) |

180nm |

180nm |

|

ولتاژ منبع تغذیه (VDD) |

1.8 Volts |

1.8 Volts |

|

عرض |

Pmos(4um) Nmos(2um) |

Pmos(4um) Nmos(2um) |

|

زمان افزایش (I / P 10P) |

0.03475ns |

0.006715ns |

|

زمان سقوط (I / P 10P) |

0.03315ns |

0.02809ns |

|

تاخیر انتشار (I / P 0) |

0.02230022ns |

0.016052ns |

|

اتلاف توان |

7’1817942*10^-12 W |

2.7257037*10^-11 W |

|

تعداد ترانزیستورها |

4 |

5 |

نتیجه

ترانزیستورها در گیت هایی که توسط منطق ترانزیستور گذر طراحی شده اند از تعداد ترانزیستورهای استفاده شده در طراحی منطق CMOS کمتر هستند. با توجه به معادله (1) با کاهش تعداد ترانزیستور، اتلاف توان کلی دستگاه نیز کاهش می یابد. اتصالات در مدار به حداقل می رسند، به این ترتیب تاخیر انتشار در اتصالات به حداقل میرسد. مشکل PTL بازسازی سطح خروجی است که منجر به کاهش حاشیه نویز می شود.

منابع:

Journal Papers

[1] IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 7, JULY 1997.

Books

[2] N. Weste, K. Eshranghian, Principles of CMOS VLSI Design: A System Perspective, Reading MA:

Addison-Wesley, (1993).

[3] Sung-Mo Kang, Y. Leblibici, CMOS Digital Integrated Circuits: Analysis and Design, Addition-Tata

McGraw Hill,(2003).

[4] Synopsys Inc, Library Compiler User Guide, Volume II, Chapters I – III, 1999

Theses

[5] Comparison between nMOS Pass Transistor logic style vs. CMOS Complementary Cells, Rakesh Mehrotra,

Massoud Pedram Xunwei Wu Dept. of E.E.-Systems

Proceedings Papers

[6] M. Cheng, M. Irwin, K. Li, and W. Ye, “Power Characterization of Functional Units,

“Conference Record of the Thirty-Third Asilomar Conference on Signals, Systems, and Computers, IEEE,

Vol.1, pp. 775-779, 1999

[7] M. A. Cirit, “Characterizing a VLSI Standard Cell Library,” Proceedings of Custom Integrated Circuit

Conference, IEEE, pp. 25.7.1-25.7.4, 1991

[8] J.F. Croix and D.F. Wong, “A Fast and Accurate Technique to Optimize Characterization Tables for Logic

Synthesis,” Proceedings of Design Automation Conference, IEEE, pp. 337-340, 1997

[9] Jing-Yang Jou, Jing-Yuan Lin and Wen-Zen Shen, “A Power Modeling and Characterization Method for

the CMOS Standard Cell Library,” Digest of Technical Papers, International Conference on Computer

Aided Design, IEEE, pp. 400-404, 1990

[10] Dhimant Patel, “CHARMS: Characterization and Modeling System for Accurate Delay Prediction of

ASIC Designs,” Proceedings of Custom Integrated Circuit Conference, IEEE,pp. 9.5.1-9.5.6, 1990

[11] Arun Pratap Singh Rathod, Brijesh Kumar, S. C. Yadav and Poornima Mittal, “Low power VLSI design

using pass transistor logic”, National Technical Expo. 2014, Jointly by NRDC New Delhi and Graphic Era

University Dehradun, at Dehradun, India, April-26-27, 2014.